Kioxia presenta la décima generación de memoria 3D FLASH BiCS de Kioxia, hasta 4,8 GT/s

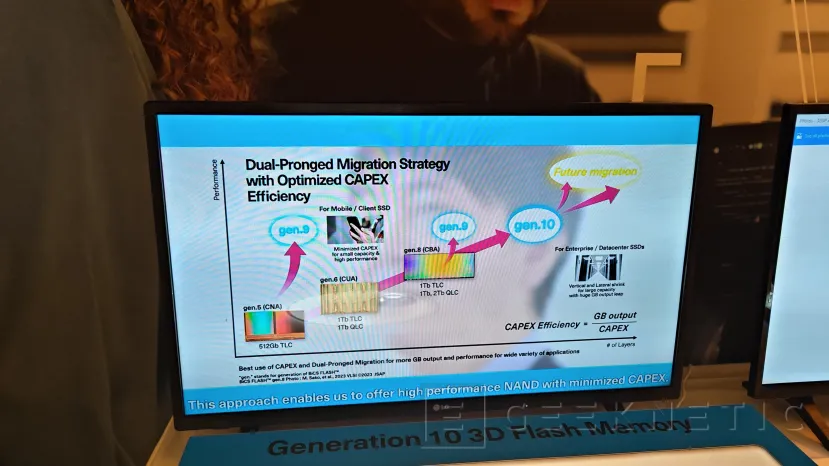

por Juan Antonio Soto Actualizado: 07/01/2026 CES 2026Para la nueva generación de discos SSD, Kioxia sigue avanzando en cuanto al diseño de sus celdas de memoria con tecnología exclusiva BiCS FLASH. El fabricante ha aprovechado este CES 2026, donde además de algunas novedades también relacionadas con el almacenamiento SSD, para presentar su décima generación de este tipo de memoria exclusiva del fabricante japonés. La décima generación de las 3D BiCS FLASH cuenta con 332 capas y la tecnología CBA que ya estaba presente en anteriores generaciones.

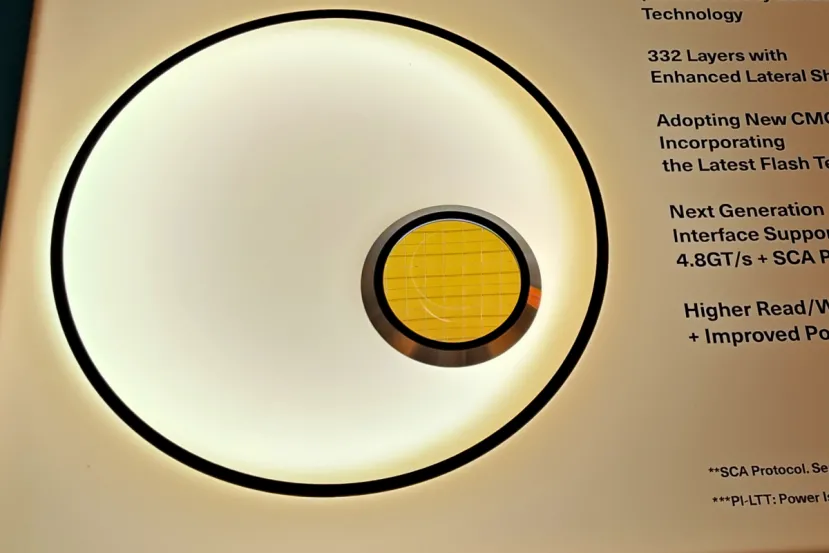

Nuevas celdas de memoria 3D FLASH BiCS de Kioxia con 332 capas

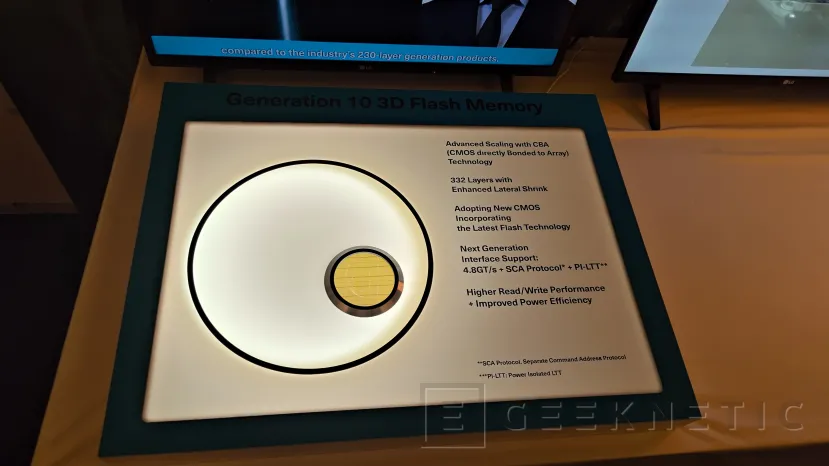

Para dar vida a la próxima generación de discos SSD, tanto para servidores y centros de datos, como para soluciones de almacenamiento destinadas a consumo, Kioxia nos muestra las ventajas de esta décima generación de memorias 3D BiCS FLASH. El fabricante sigue trabajando para añadir y mejorar su tecnología CBA (CMOS directamente a la matriz). Además, esta generación ha conseguido 332 capas incluso con una reducción lateral mejorada, con un menor número de capas efectivas por bit.

La décima generación de memorias BiCS FLASH ofrecen hasta 4,8 GT/s

Con estas memorias se podrán construir discos de próxima generación, ya que ofrecen hasta 4,8 GT/s para un mayor rendimiento de lectura y escritura. También cuenta con mejor eficiencia energética, muy importante en estos tiempos en los que un menor consumo favorece a este tipo de componentes. Se espera que se comience a fabricar en masa aproximadamente en un año, os dejamos las características completas.

Tecnología de fabricación

- Escalado avanzado con tecnología CBA (CMOS directly Bonded to Array — CMOS directamente unido a la matriz de memoria)

- 332 capas con reducción lateral mejorada (Enhanced Lateral Shrink)

- Uso de nuevo CMOS que incorpora la tecnología Flash más reciente

Interfaz de nueva generación

- Soporte para interfaz de próxima generación:

- 4,8 GT/s

- Protocolo SCA (Separate Command Address Protocol)

- PI-LTT (Power Isolated Low Threshold Transistor)

Rendimiento y eficiencia

- Mayor rendimiento de lectura y escritura

- Mejor eficiencia energética

Objetivos de fabricación

- Reducción del CAPEX (costes de inversión en fabricación)

- Menor número de capas efectivas por bit gracias al escalado lateral

Notas técnicas

- SCA Protocol: protocolo que separa las direcciones de comando para mejorar paralelismo.

- PI-LTT: transistores de bajo umbral con aislamiento de potencia para reducir consumo.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!