AMD trabaja en implementar DRAM y SRAM apilada en 3D en sus procesadores utilizando un esquema vertical

por Sergio San Joaquín 1

AMD está trabajando actualmente en la implementación de DRAM y SRAM apilada en 3D, en una próxima generación de procesadores Ryzen con el objetivo en mente de aumentar su rendimiento.

Si hay una cosa que no se le puede negar a AMD recientemente es su perseverancia en innovar tecnología que aumente el rendimiento de sus productos, el conjunto de multi chips distribuidos en el die, o comúnmente conocido como chiplets fue una acertada solución que abrió el camino para poder producir CPUs de múltiples cores.

Los chiplets son un conjunto de chips más pequeños interconectados entre sí por el Infinity Fabric (bus de conexión interna desarrollada por AMD), que eliminan posibles defectos de silicio en chips de mayor tamaño y reducen el coste de fabricación, cada chiplet se comunica con la RAM del sistema , y aunque no es una solución aun perfecta, ya que por ejemplo los 32 cores del Threadripper 2990WX no disponen de un canal de RAM para cada chiplet, ya que usa Quad Channel (no así como su versión server, EPYC) y además esto provocó que se vieran afectadas sensiblemente las latencias.

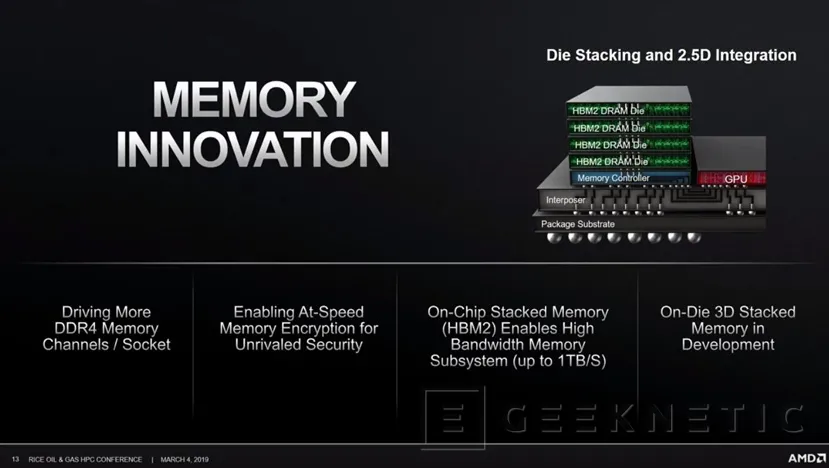

Fue, sin embargo, un gran avance que trataba de “luchar” contra la ley de Moore, y ahora se pretende dar un nuevo paso adelante con la implementación de DRAM/SRAM.

Intel no se queda atrás, y recientemente anunció su tecnología Foveros 3D, en el cual se verá una CPU fabricada en 10 nm junto con un I/O chip interconectado con TSV (a través de Silicon Via), su diseño difiere no obstante del de AMD, ya que Intel ha diseñado un sistema en capas una encima de otra con un chip en la parte superior que utiliza el sistema PoP (Package on Package) convencional, conectando la memoria DRAM a través de dos filas adicionales con conexión BGA que rodean al chip subyacente transfiriendo los datos entre chips, pero sin estar los dies conectados directamente.

Sin embargo, AMD está pensando en un sistema 3D real, lo que quiere decir que se juntarían 2 dies (por ejemplo, DRAM + CPU) colocadas una encima de la otra conectadas verticalmente por TSV los cuales acoplan los dies entre sí, el acoplamiento directo reduciría el consumo de energía, latencia, y ofrecería ventajas de densidad.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!