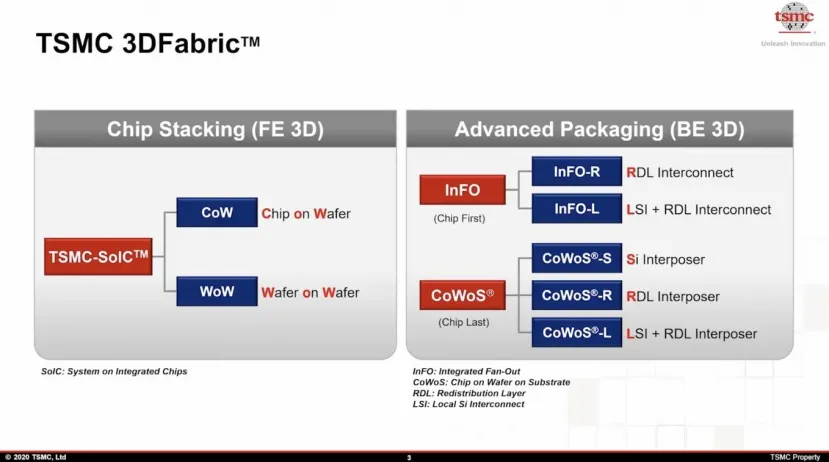

TSMC ha explicado en el último Technology Symposium los avances que ha estado realizando en cuanto a tecnología de empaquetado de chips y ha presentado sus tecnologías de empaquetado de chips apilados bajo la nomenclatura 3DFabric. Esta tecnología compite con otras como por ejemplo Intel Foveros.

En el caso de TSMC, eso sí, 3DFabric es una nomenclatura para un total de tres tecnologías, entre las que encontramos fabricación 2.5D y 3D, de modo que tanto podemos encontrarnos con los dies de silicio apilados unos sobre otros, como con los dies conectados a través de un interponedor, siendo una aplicación habitual de estas tecnologías la de la memoria HBM, la cual llega en forma de varios dies apilados, para después conectarse a una GPU con un interponedor sobre el sustrato del chip.

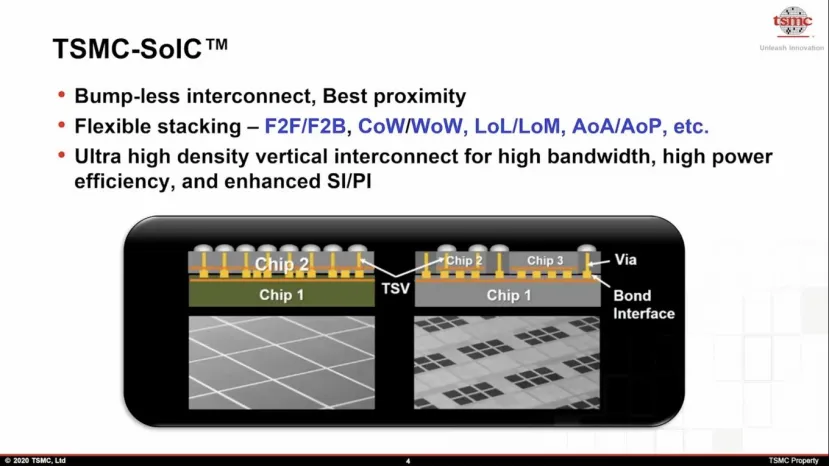

En el caso del apilado de TSMC, bajo el nombre SoIC (System on Integrated Chips), encontramos dos variantes llamadas CoW (Chip-on-Wafer) y WoW (Wafer-on-Wafer), algo que deriva en toda una estructura de distintos empaquetados de chips, tal y como vemos en la imagen.

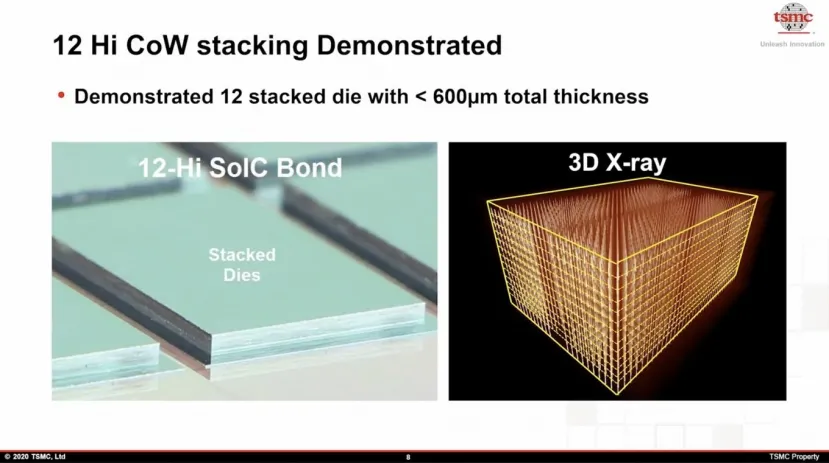

En el caso del TSMC-SoIC, podemos ver como se trabaja con una tecnología bump-less que permite aumentar la proximidad de los chips, algo que a las velocidades a las que se trabaja en la interconexión de chips, es importante a la hora de reducir por ejemplo la latencia, además de aumentarse la densidad de conexiones que lleva a un aumento del ancho de banda entre los dies apilados. En la demostración realizada por la compañía, se ha mostrado un conjunto de 12 dies apilados con un grosor total inferior a los 600 micrómetros o 0.6 milímetros.

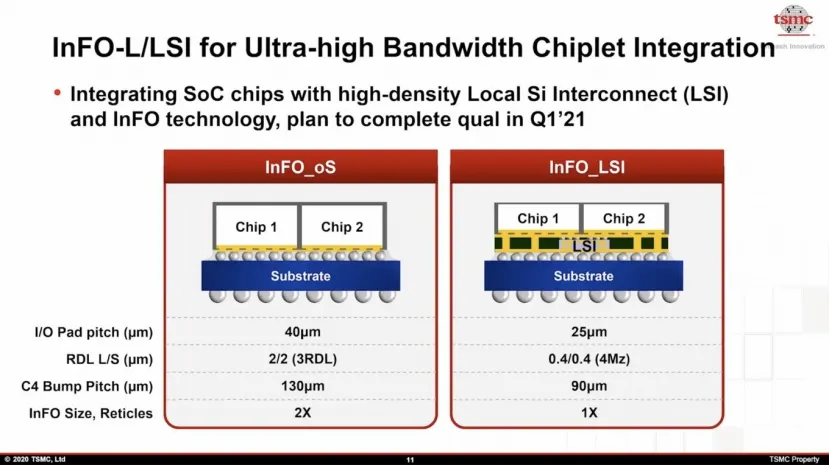

Otras tecnologías como TSMC-InFO-L/LSI permiten una integración de chiplets de ultra alto ancho de banda, similar a la Infinity Fabric de AMD, con una interconexión de silicio que permite que los chips puedan conectarse a través de pads de tan solo 25 micrómetros, aumentando de nuevo el ancho de banda en el mismo tamaño y una reducción a la mitad del tamaño del conjunto.

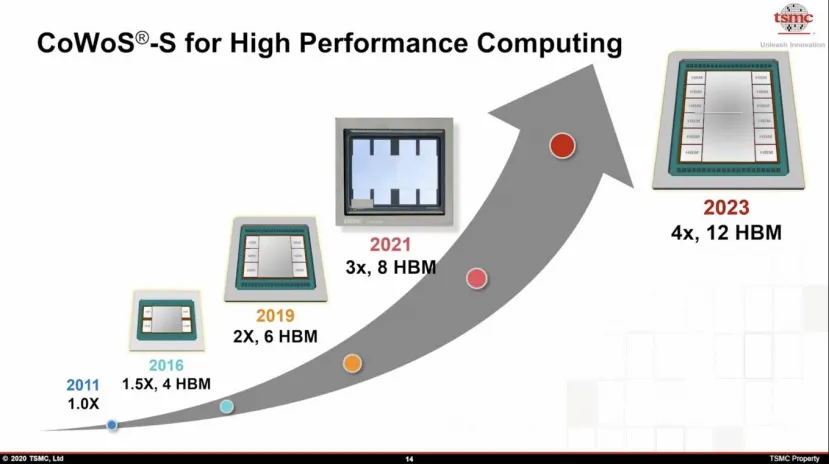

Por su parte, CoWoS-S está orientado a la computación de alto rendimiento, con objetivos que, tal como vemos, apuntan a un tamaño de retícula 4 veces mayor con 12 chips HBM para 2023, llevándonos a una posible era de GPUs multi die de alto rendimiento.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!