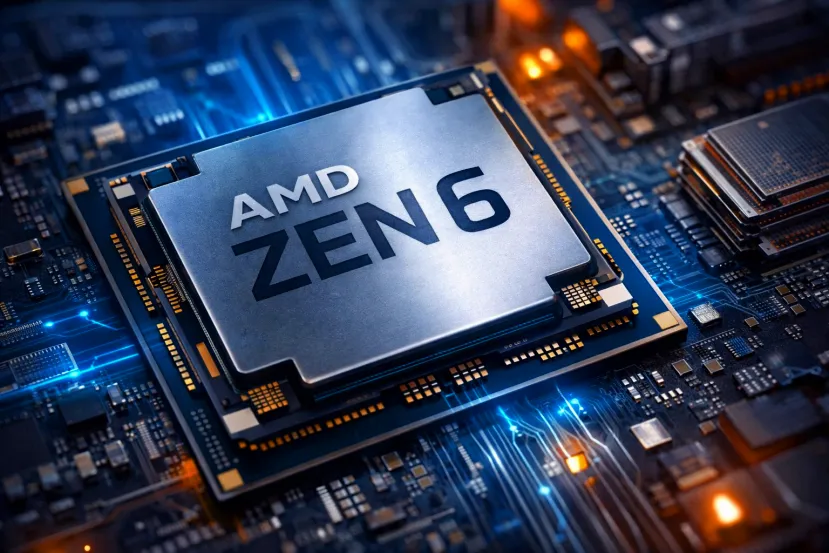

AMD mueve ficha en Zen 6 12 núcleos en un solo CCD y 48 MB de caché L3 para escalar más fácil

por Manuel Naranjo 2Hay un tipo de dato que, cuando se filtra, no suena a titular vistoso, pero en el mundillo del hardware actúa como una piedra en el estanque. Un número pequeño que empieza a dibujar ondas. En este caso, lo que se ha conocido sobre Zen 6 no es una frecuencia récord ni un nombre comercial, sino algo más “de cimientos”: el diseño del CCD, el chiplet donde viven los núcleos.

La información que ha salido a la luz señala que el próximo CCD de Zen 6 daría el salto a 12 núcleos manteniendo 48 MB de caché L3. Para el lector que no esté metido hasta las cejas en procesadores, la traducción rápida es esta: AMD estaría intentando meter más músculo en cada pieza del puzle sin disparar el tamaño de la caché principal del chiplet. Y eso, en una arquitectura basada en chiplets, tiene implicaciones directas en rendimiento, costes y, sobre todo, en cómo se colocan las gamas Ryzen y EPYC en el tablero.

Qué significa que un CCD pase de 8 a 12 núcleos

Hasta ahora, el patrón más reconocible en AMD era claro: un CCD típico agrupa 8 núcleos con 32 MB de L3 en las generaciones recientes, mientras que el resto del procesador se completa con el dado de entrada y salida y, si toca, más CCD. Ese enfoque modular ha sido uno de los grandes “secretos” del éxito de Ryzen y EPYC: fabricar chiplets relativamente pequeños y combinarlos según el producto final.

Si el salto a 12 núcleos por CCD se confirma como base en Zen 6, cambia el reparto de piezas. Con un chiplet más denso, AMD puede construir procesadores de más núcleos con menos chiplets, o mantener el número total y escalar aún más arriba. En términos prácticos, un Ryzen de escritorio que antes necesitaba dos chiplets para llegar a 16 núcleos, con un diseño de 12 núcleos por chiplet abre otras combinaciones y deja más margen para segmentar modelos sin repetir exactamente el mismo esquema generación tras generación.

El impacto es aún más evidente en servidor. EPYC vive de sumar chiplets como quien apila ladrillos, y un ladrillo más grande significa que el “muro” final puede levantarse con menos piezas, o con más altura manteniendo un recuento razonable de chiplets. Y ahí AMD suele jugar con dos ideas: densidad y eficiencia.

La caché L3 se queda en 48 MB y eso también dice mucho

A primera vista, lo de 48 MB de L3 parece un número raro, porque no es el clásico 32 MB del chiplet de 8 núcleos. Pero encaja con una lógica sencilla: si aumentas núcleos, necesitas más caché para alimentar ese bloque sin que se pase el día yendo a memoria principal. En Zen 5, por ejemplo, el CCD estándar mantiene 32 MB de L3 para 8 núcleos, con configuraciones especiales que añaden caché extra mediante apilado.

La clave aquí está en el equilibrio. Subir la caché ayuda, sí, pero también ocupa área en el silicio y complica el diseño. La filtración sugiere que AMD habría elegido 48 MB como punto intermedio: más caché por chiplet para acompañar el aumento de núcleos, pero sin hacerla tan grande como para condicionar costes o rendimientos de fabricación.

Dicho de otra forma, Zen 6 estaría apostando por un chiplet más “nutrido” por dentro, pero todavía razonable en tamaño. Y eso suele ser una pista de cómo quiere competir AMD en precios y volúmenes.

Rendimiento real el tipo de mejora que se nota sin mirar el contador de FPS

Este tipo de cambios no va de un pico espectacular en un benchmark concreto. Va de la mejora silenciosa que se cuela en muchos escenarios: compilación, render, cargas mixtas, multitarea pesada, virtualización doméstica, y también juegos, aunque ahí el comportamiento es más caprichoso.

Más núcleos por CCD significa que, en cargas multihilo, hay más trabajo hecho “dentro” de una misma isla de silicio. Y al mantener una L3 relativamente amplia, se reduce el riesgo de que esos núcleos se estorben o se queden esperando datos. No es solo cuestión de potencia bruta, también de latencias, coherencia y de cómo se reparten los hilos entre chiplets.

Qué puede cambiar en la gama Ryzen y en los planes de AMD

Si el CCD de 12 núcleos se convierte en el bloque estándar, AMD gana flexibilidad para construir familias muy distintas con la misma base. En escritorio, podría permitir modelos de 12 núcleos de una sola pieza o configuraciones de 24 núcleos con dos chiplets, si el mercado lo pide. En portátiles, el enfoque suele ser distinto, pero la idea de densidad siempre tienta cuando se busca rendimiento por vatio.

En servidor, el impacto es casi inevitable: EPYC compite en recuento de núcleos, ancho de banda de memoria y eficiencia. Un chiplet más denso permite mover el listón sin rediseñar todo el ecosistema. Y, a nivel industrial, también ayuda a ajustar la producción, porque reduces el número de chiplets necesarios por CPU final en determinadas gamas.

Lo interesante es que esta filtración llega en un momento en el que el sector se está poniendo serio con la computación para IA y con cargas de trabajo que castigan muchísimo la memoria y las latencias. Más núcleos por chiplet y una L3 más grande no solucionan todo, pero sí dibujan una estrategia: más densidad, más coherencia interna y una base con margen para variantes.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!