La realidad sobre los nanómetros en procesos de fabricación de CPUs y GPUs

por Mikel Aguirre Actualizado: 25/04/2024 26Distribución del mercado de semiconductores

Prácticamente desde la invención del circuito integrado semiconductor a finales de los años 50, la informática y la tecnología giran inevitablemente en torno a la industria de los semiconductores.

Un semiconductor es un elemento capaz de cambiar su conductividad eléctrica en función de diversos factores como por ejemplo la aplicación de un campo magnético, campo eléctrico, la presión, etc. El material semiconductor más usado en el mundo tecnológico es el silicio.

Los productos semiconductores abarcan todos los procesadores, GPUs y SoCs, sean AMD, Intel, NVIDIA, Qualcomm, Mediatek, Samsung, etc. Por si esto fuera poco también los son todos los chips de algún tipo, chipsets de placas base, chips de sonido, chips controladores de ethernet, chips de memoria RAM, los chips NAND de los SSD, centralitas de los coches, TVs, equipos de música y hoy en día, gracias al Internet del as cosas, hasta tu lavadora y tu tostadora es probable que tengan microchips semiconductores.

En el mundo de los semiconductores diferenciamos dos tipos de empresas:

- Arquitectos: el que diseña el chip, su arquitectura, la distribución de los transistores, la caché necesaria, etc. Generalmente los arquitectos también son encargados de comercializarlos y desarrollarlo como solución completa con el firmware o el software que requiera. Ejemplos: AMD, NVIDIA, Qualcomm, Mediatek, etc.

- Fundiciones: Son empresas menos conocidas responsables de fabricar los chips diseñados por los arquitectos.

Fábrica fundición de Intel

Por poner un ejemplo, los ingenieros de NVIDIA diseñan su arquitectura Pascal para tarjetas gráficas y otros dispositivos. Su experiencia en el sector y la agudeza de sus ingenieros les permite trabajar en la arquitectura a fondo para conseguir una relación de rendimiento por vatio nunca vista en tarjetas gráficas hasta ahora. Sin embargo, los chips son fabricados por TSMC en un proceso dicen es de 16nm, cuya tecnología es propietaria de TSMC.

Esto supone que las empresas de semiconductores que no tienen fundición, es decir, la inmensa mayoría salvo casos especiales como Intel o Samsung, dependen en gran medida de las tecnologías y procesos de fabricación que les ofrece la fundición que al fin y al cabo fabrica su chip.

Volviendo al ejemplo anterior, por muy bien hecha que esté la arquitectura de NVIDIA, ésta ha sido desarrollada teniendo en cuenta las propiedades del proceso de producción a 16nm de TSMC, que juega un papel vital en el éxito de NVIDIA en la obtención de dicho rendimiento por vatio con su arquitectura.

Aunque empresas de tipo “Arquitectos” que diseñan sus propias arquitecturas hay muchas, la fabricación de los chips de todas esas empresas se reparte principalmente entre tan solo 4 grandes fundiciones a nivel mundial debido a que son los únicos fuertemente preparados tanto a nivel de tecnologías de fabricación como en capacidad de producción:

- Intel: el gigante de los procesadores que tiene sus propias fábricas, apodado como “chipzilla”. Ahora de hecho también fabrican para terceros.

- Global Foundries: Las antiguas fábricas de AMD que ahora pertenecen a este consorcio y sigue teniendo una estrecha relación con el mismo. Todos los procesadores de la arquitectura Zen de AMD los fabrica Global Foundries y así es también con los chips gráficos Vega.

- TSMC: Fabricante taiwanés que fabrica todo tipo de chips para multitud de empresas como NVIDIA, Apple, Mediatek, etc.

- Samsung: El conocido conglomerado gigante de los smartphones, fabricante de TVs y otros productos de consumo dispone también de una división con fábricas propias dedicadas a la producción de semiconductores. Producen por ejemplo los procesadores Exynos que llevan algunos smartphones Samsung, aunque también fabrican para terceros, como por ejemplo para Qualcomm.

Es importante destacar que progresar en los procesos de fabricación de semiconductores es tremendamente complejo, equiparable por ejemplo a progresar en aeronáutica. El I+D necesario para mejorar es gigante y la maquinaria e instalaciones necesarias requieren de una inversión grande y constante. Por poner un ejemplo, Intel está invirtiendo 7 mil millones de dólares en su nueva fábrica para los chips que fabriquen en un futuro basados en un proceso de fabricación de 7nm. Cada paso adelante en el proceso de fabricación puede suponer la diferencia entre estar en pérdidas o tener un negocio tremendamente lucrativo, así de competitivo y duro es el mercado.

Esto hace que tan solo estas 4 empresas gigantes y con grandes recursos sean las que consiguen hoy en día ser relevantes como fundiciones de semiconductores.

Un caso aparte a destacar es ARM, que aunque puede considerarse un arquitecto, realmente no comercializan chips. Se dedican a diseñar los chips y vender y licenciar sus arquitecturas a otros arquitectos como Qualcomm, HiSilicon de Huawei, Mediatek y otros tantos.

Cómo se fabrica un chip de silicio

Actualmente el estándar de fabricación, en obleas (wafers) de silicio, está basado principalmente en un sistema que se llama Fotolitografía. La fotolitografía comparte el mismo principio básico que la litografía.

La litografía es un antiguo proceso que existió antes de la invención de la imprenta que funcionaba del siguiente modo: se creaba una piedra grabada con la imagen que se deseaba replicar, se ponía una hoja de papel encima y se pasaba una pintura por encima, dejando grabada en el papel la imagen idéntica que se ha tallado en la piedra, permitiendo hacer copias exactas.

La litografía despareció con la invención de la imprenta, sin embargo, la fotolitografía en semiconductores usa un principio muy similar. En la fotolitografía de semiconductores la piedra vendría a ser un filtro o máscara fotográfica con el diseño del chip a fabricar. Se apunta un haz de luz hacia la oblea de silicio y entre ambos se coloca dicho filtro fotográfico.

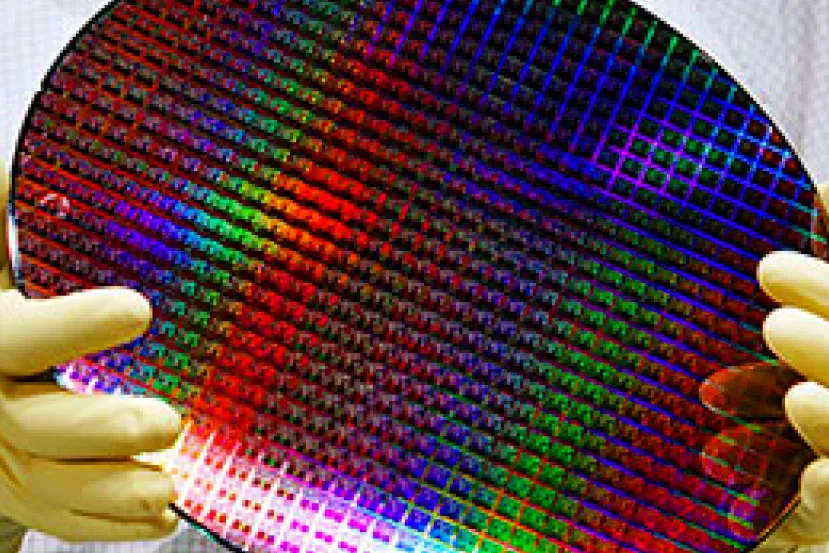

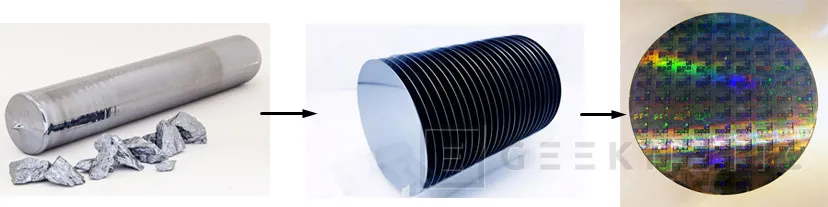

La oblea de silicio, también conocida como sustrato en la industria, es una finísima capa circular de silicio en la cual se “graban” muchos chips idénticos al mismo tiempo.

A la izquierda un tubo de silicio, que se corta en obleas vírgenes que vemos en el centro. A la derecha la oblea procesada en que cada cuadro es un chip.

El proceso podemos resumirlo a grandes rasgos en los siguientes pasos:

- El diseño del chip con todos sus transistores se graba en forma inversa en un filtro fotográfico, también llamado máscara, que es similar a una diapositiva.

- De un tubo de silicio se corta una rodaja finísima que vendrá a ser la oblea.

- La oblea recibe un tratamiento químico para limpiar impurezas y se calienta para hacer que sea perfectamente uniforme.

- Se unta la oblea de silicio con una fina capa de un material que reacciona a la luz, que llamaremos a partir de ahora “fotorresistente”.

- Se proyecta un haz de luz de baja amplitud de onda (generalmente ultravioleta) a través del filtro hacia la oblea.

- Las partes del fotorresistente expuestas a la luz, teniendo en cuenta la máscara o filtro fotográfico aplicado sufren un cambio químico.

- Un torno hace girar la oblea a unas revoluciones fijas.

- Mientras está girando se vierte sobre la oblea una solución química que “revela” o elimina el material fotorresistente que ha sufrido dicha la transformación química. Por tanto, ahora ya tenemos la oblea cubierta exactamente con el diseño del chip a escala nanométrica.

- Se mete la oblea un horno a temperaturas de 120ºC a 180ºC que solidifica el “fotorresistente” restante con la forma del chip.

- Un agente químico elimina la capa superior de silicio allá donde no está protegida por dicho fotorresistente solidificado, grabando definitivamente en el silicio la forma del chip.

- Habiendo grabado ya el chip en el silicio, el fotorresistente deja de ser necesario y se utilizan otros materiales químicos para eliminarlo.

- Se comprueba la conductividad de cada uno de los chips fabricados ya que hay grandes diferencias entre los chips de una misma oblea, pese a que todos tengan el mismo diseño. Esto se hace a fin de identificar los mejores y poder clasificarlos para un producto final u otro.

- Se cortan los chips de la oblea.

- Se ensamblan los chips con sus correspondientes encapsulados, pines de contacto o circuito integrado que le corresponda.

La inmensa mayoría de chips que se fabrican hoy en día se hacen usando esta metodología. Una de las claves está en el uso de fuentes de luz que emitan una luz con menor longitud de onda (UV generalmente), ya que a menos longitud de onda más precisión tiene la luz y más nítidos y perfectos son los grabados en el material fotorresistente, permitiendo crear un tamaño de transistor más pequeño.

Un tamaño de transistor más pequeño significa a fin de cuentas que en un mismo espacio podemos meter más transistores. Más transistores en un mismo espacio significa más rendimiento por vatio en ese espacio y el arquitecto puede jugar para dar más rendimiento con el mismo consumo o bien mismo rendimiento con menos consumo.

Esto es a lo que los fabricantes intentan referirse cuando nos hablan de que sus procesadores, GPUs o chips de cualquier tipo han sido fabricados bajo un proceso de fabricación que definen en nanómetros. Por ejemplo, AMD anuncia que su arquitectura Zen ha sido fabricada con un proceso de fabricación de 14nm, lo mismo con su arquitectura gráfica Vega, ambas fabricadas por la fundición Global Foundries. Lo mismo con NVIDIA y sus chips gráficos Pascal fabricados a 16nm de TSMC, y lo mismo con el resto de fabricantes.

¿Pero a qué hacen referencia exactamente esos 14nm o 16nm? Veámoslo en el siguiente apartado.

El tamaño en nanómetros de los procesos de fabricación

Durante muchos años el estándar de la industria de los semiconductores con respecto a medir el tamaño en procesos de fabricación seguía el patrón marcado por la fabricación de celdas de memoria, lo que se conoce como DRAM Half Pitch.

Miremos con microscopio un conjunto de celdas de memoria DRAM y escojamos un punto concreto dentro de una de las celdas. Ahora nos fijamos en exactamente el mismo punto en una celda contigua y medimos la distancia que nos da en micrones o en nanómetros. Dividimos por la mitad dicha distancia y obtenemos el DRAM Half Pitch.

Esto se usaba de esta forma: si una fundición conseguía una técnica por la cual era capaz de fabricar celdas de memoria a un DRAM Half Pitch 125 nanómetros, se decía que todo chip lógico o procesador que fabricara usando esa misma técnica tenía un proceso de fabricación de 125 nanómetros; dicho de otra forma, esa fundición tenía un “Technology Node” de 125 nanómetros.

El problema es que hace unos años se alcanzó el límite al cual se podían reducir las celdas de memoria, al tiempo en que se seguía pudiendo disminuir el tamaño de los transistores de los procesadores. Por este motivo hace años que las celdas de memoria dejaron de ser el estándar para los procesos de fabricación. Tampoco ayudó el hecho de que la forma en que se desarrollan los chips de todo tipo hoy en día y la forma que tienen y en que se disponen los transistores no tiene ya nada que ver con aquellos tiempos. Desde entonces no existe un consenso entre las fundiciones para un estándar a la hora de definir sus procesos de fabricación y digamos que cada cual lo indica a su manera.

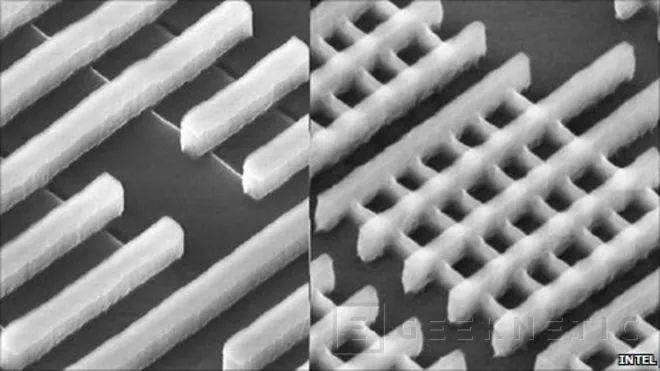

Comparación entre transistores planos tradicionales (izquierda) y los primeros transistores Tri-Gate de Intel (derecha)

A esto tenemos que añadirle que cada “arquitecto” dibuja los transistores a su manera, hay quien mete 6 puertas lógicas por transistor, hay quien hace las puertas más grandes, etc., por tanto, el tamaño del transistor tampoco puede tomarse como referencia.

Por todos estos motivos hace ya muchos años que el número de nanómetros dejo de ser un número real y cayó en manos de los departamentos de marketing de las fundiciones. En pocas palabras, que cuando Intel, AMD, NVIDIA, etc. nos hablan de que sus procesadores o chips son de 14 nanómetros, en realidad no hay nada en sus chips que mida 14 nanómetros. Las fundiciones, a falta de un estándar intentan acercarse a lo que sería el equivalente si las celdas de memoria siguieran siendo el estándar, no obstante, la realidad es que sus intereses en marketing gobiernan por encima de ello. Si Global Foundries, TSMC e Intel, ambos ofrecen procesos de fabricación a los que llaman 14nm, la realidad es que probablemente haya grandes variaciones en los tamaños de los componentes de los transistores de unos a otros y por tanto en la densidad de transistores de los chips que fabrican.

Hoy en día esto ocurre con todas y cada uno de las fundiciones y las empresas de semiconductores sin excepción. Intentan jugar con ello en su beneficio por las ventajas que les pueda suponer en marketing y en ventas llamar a su tecnología con un número en nanómetros frente a otro.

¿Entonces cómo podemos saber quién es capaz de fabricar chips con más cantidad de transistores en un mismo espacio y conocer las diferencias reales entre fundiciones?

Es difícil saberlo con exactitud, sin embargo, la respuesta más cercana nos la proporciona la fórmula ASML.

En el siguiente apartado tratamos la fórmula a fondo.

Fórmula ASML

ASML es un fabricante holandés responsable de desarrollar y proporcionar la maquinaria y las soluciones fotolitográficas que utilizan todas las fundiciones importantes del mundo, especialmente las 4 más grandes citadas al comienzo del artículo.

ASML conoce el proceso litográfico mejor que nadie y, en vista de que el tema de los números usados al llamar a los procesos de fabricación se ha ido bastante de madre y cada fundición dice lo que le parece, a fin de armonizar la industria desarrollaron hace uno años una fórmula capaz de comparar en términos cercanos a la realidad el proceso de fabricación de las fundiciones: La Fórmula ASML.

Nodo Estándar = 0.14 x (CPHP x MMHP)0.67

Ya que cada fundición tiene variaciones en la forma en que obtienen sus adelantos tecnológicos en procesos de fabricación, ASML introdujo en su fórmula el concepto de “nodo estándar”. Aunque no es una medida en sí misma, se obtiene aplicando a la fórmula las mediciones reales CPHP y MMHP. El “nodo estándar” que obtenemos en la formula nos proporciona por tanto una visión de cómo de tecnológicamente avanzadas se encuentran cada una de las fundiciones, independientemente de la forma en que avancen tecnológicamente.

Para poder entender la fórmula ASML, primero tenemos que entender los 2 tipos de mediciones de los que se compone: el CPHP y el MMHP.

CPHP

A día de hoy un transistor típico de un procesador está formado por unas tiras de silicio por las que viajan los electrones. Estas tiras están conectadas a un extremo origen que emite los electrones y un extremo final que los recoge. Al mismo tiempo dichas tiras están atravesadas por una o varias puertas lógicas que corta el paso a los electrones de un extremo a otro. Dependiendo de si la puerta lógica está abierta o cerrada se determina el estado de la tira. Tenemos por tanto dos estados: cerrado y abierto, o lo que es lo mismo, 0 y 1 respectivamente.

La distancia conectada que se puede conseguir entre la tira, la puerta lógica y sus extremos es el “Connected Poly Pitch” y la mitad de ello es el “Connected Poly Half Pitch” o el CPHP de la fórmula.

MMHP

El acrónimo en inglés es Minimum Metal Half Pitch. Trata de la distancia mínima conseguible entre las conexiones que conectan cada transistor o parte del transistor al resto del chip.

Importante: Ni el MMHP, ni el CPHP, ni el nodo estándar, y mucho menos el proceso de fabricación que anuncian las fundiciones hacen referencia al tamaño de los transistores. Los transistores, dentro de una misma fundición, incluso dentro de un mismo chip adopta formas y tamaños muy distintos, en función de cómo el arquitecto los haya dibujado. MMHP y CPHP son mediciones reales de partes de los transistores y otros elementos del chip.

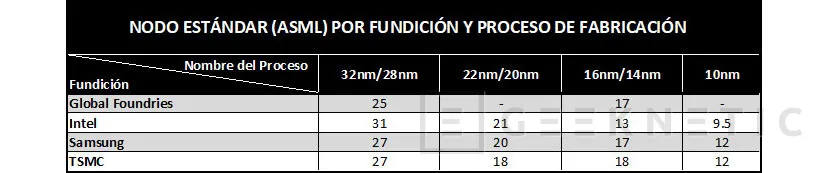

Ahora si aplicamos las mediciones reales a la fórmula con respecto a los procesos de fabricación en nanómetros con las que las fundiciones publicitan sus fábricas y servicios obtenemos los siguientes resultados:

Ahora tenemos por tanto una forma más realista de comparar los procesos de fabricación de las fundiciones y los chips que salen de ellas. Si cogemos los procesadores Skylake, Kaby Lake, Kaby Lake-R o Coffee Lake de Intel han sido fabricados, según ellos, bajo un proceso de 14nm. Aplicando la fórmula de ASML, el nodo estándar de Intel estaría en 13. Si por el contrario cogemos los 14nm de Global Foundries por el cual se fabrican los procesadores Zen de AMD y los chips gráficos Vega y Polaris, nos encontramos que el nodo estándar se sitúa en 17.

Podemos determinar por tanto que por mucho que Intel y Global Foundries anuncian que sus procesos son de 14nm, hay una diferencia de 4 puntos entre ellos al comparar el resultado de la fórmula. Se trata de más de un 20% de diferencia, lo cual en el mundo de los transistores es una inmensidad. Esto significa que Intel tendrá muchas más facilidades para lograr mayor densidad de transistores en sus chips y por tanto mayor rendimiento por vatio pese a que ambos lo anuncien como procesos de 14nm. Además, podemos apreciar que Intel es la única fundición que con el nombre que dan al proceso de fabricación tienden a acercarse más al nodo estándar de la fórmula ASML.

Otra cosa ya es que las arquitecturas de AMD, la forma con la que diseñan los transistores y los implementan en sus chips lleven a compensar esto de alguna manera. No obstante, no podemos evitar pensar que Intel va un paso por delante en cuanto a su tecnología en el proceso de fabricación y puede guardarse ases bajo la manga para ofrecer productos más eficientes o más potentes cuando lo deseen.

No obstante, es posible que la clara ventaja con la que goza Intel en sus procesos de fabricación con respecto a otras fundiciones no dure para siempre. Analizamos este asunto en los siguientes apartados.

El fin del Tick-Tock y de la Ley de Moore

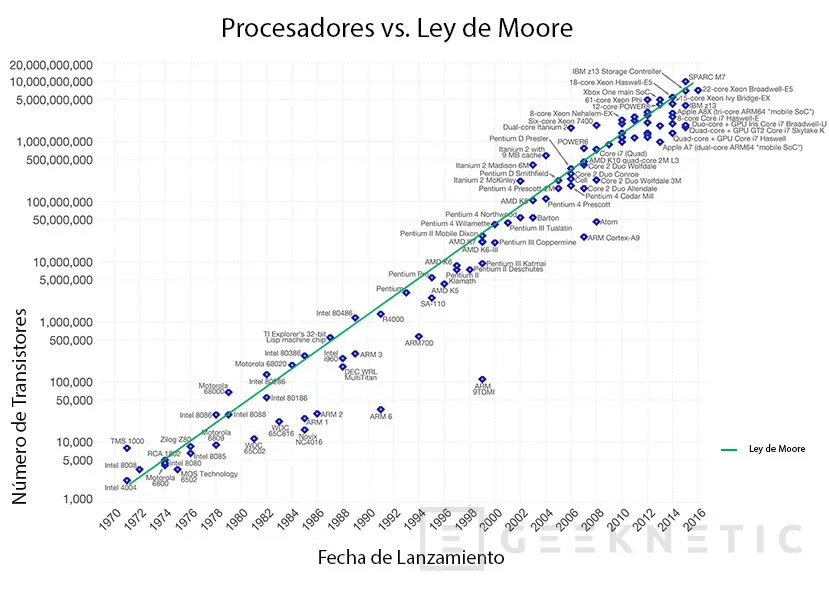

Gordon Moore, co-fundador de Intel y presidente de la misma durante muchos años, realizó una predicción, muy famosa en el sector, llamada “La Ley de Moore”. La predicción consiste en que la cantidad de transistores que se pueden integrar en un chip se duplica cada 2 años.

Con el paso de los años se ha visto sobradamente demostrada la ley hasta tal punto que toda la industria de semiconductores la ha utilizado para planificar sus roadmaps y sus futuros productos.

Si bien en el gráfico de arriba se puede ver lo fielmente que la industria ha cumplido la Ley de Moore, el propio Moore predijo también que el final de su propia ley se situaría al alcanzar procesos de 5nm.

A finales de 2017 nos vamos acercando ya a este momento. La realidad es que por debajo de 7nm resulta inmensamente difícil reducir los tamaños en el silicio usando las técnicas fotolitográficas que se vienen usando hasta ahora. Esto se debe a que aumenta la posibilidad de que se produzca un efecto llamado Túnel Cuántico.

En mecánica cuántica, el túnel cuántico es un efecto por el cual una partícula es capaz de cruzar una barrera que según las propiedades de la mecánica tradicional no podría cruzar. Esto aplicado a los chips de semiconductores significa que si tenemos elementos como puertas lógicas o tiras (fins) más pequeños a 1nm dentro de un transistor, algunos electrones podrían cruzar la puerta lógica pese a estar cerrada. Esto haría los transistores y el chip inservibles.

Estamos ante una de las mayores barreras tecnológicas que se ha conocido y es por esto que Intel, el líder indiscutible hasta el momento en procesos de fabricación, ha desacelerado considerablemente la velocidad de introducción al mercado de nuevos procesos de fabricación.

Antiguamente Intel introducía sus generaciones de procesadores a través de un sistema de 2 fases que ellos llamaban el Tick-Tock. El Tick introducía un nuevo proceso de fabricación bajo la misma arquitectura, como por ejemplo pasar de fabricar la arquitectura Nehalem de 45nm a 32nm. El Tock era una nueva arquitectura dentro del mismo proceso de fabricación, como fue pasar de la arquitectura Nehalem a Sandy Bridge en un proceso de fabricación de 32nm.

Debido a que se iba acercando peligrosamente a los temidos 7nm, Intel decidió romper con el Tick Tock y sacar familias de procesadores de una forma más bien arbitraria. A los saltos en el proceso en nanómetros le siguen los cambios de arquitectura y a éstos diversas optimizaciones tanto en el proceso como en la arquitectura que aprovechan para sacarse de la manga nuevas generaciones de producto a ojos del consumidor. Así en 22nm hemos visto 3 familias de producto y en 14nm ya hemos pasado por 5: Broadwell, Skylake, Kaby Lake, Kaby Lake-R y Coffee Lake, siendo las últimas 3 en realidad optimizaciones basadas en Skylake.

Tengo que decir, no obstante, que las optimizaciones que Intel empezó a introducir tras el fin del Tick-Tock le están dando buen resultado. Un claro ejemplo es que, en portátiles, al pasar de Kaby Lake a Kaby Lake-R han conseguido fabricar procesadores con un 40% más de rendimiento con exactamente el mismo consumo energético pese a ser prácticamente la misma arquitectura y tener unos ligeros cambios en el proceso de fabricación (de 14nm FF a 14nm FF+ según ellos).

El Futuro de los Semiconductores

Como hemos visto en el apartado anterior, el Tick-Tock y la Ley de Moore han llegado a su fin. En gran parte se debe a que el efecto de Túnel Cuántico dificulta enormemente rebajar el proceso de fabricación por debajo de los 7nm.

Para poder crear transistores más pequeños a partir de este punto resulta necesaria la introducción de enormes avances tecnológicos. Existen multitud de tecnologías en desarrollo en diferentes universidades y centros de investigación, algunos de ellos financiados por alguna de las 4 fundiciones. Una de las tecnologías más susceptibles de ser desarrolladas y usadas en la fabricación en masa es el EUV (Fotolitografía de Ultravioleta Extremo), que consiste en una mejora sustancial sobre las lámparas ultravioletas que se usan actualmente además de una serie de mejoras más en las fábricas. También hay mucha investigación en torno a los materiales a usar: se está estudiando por ejemplo el uso de Grafeno, Arseniuro de Indio y Galio y nanotubos de carbono como sustitutos del silicio.

Existe mucha incertidumbre con respecto a qué acabará siendo el nuevo estándar de fabricación de la industria por debajo de los 7nm. Al tiempo que se les ve tantear con una tecnología u otra, van tomando posiciones con respecto a preparar sus fábricas para los 7nm que veremos en poco tiempo, estando dentro todavía de los límites de la física cuántica que predijo Gordon Moore.

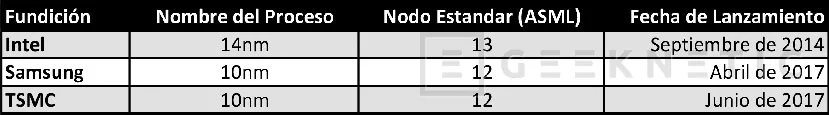

Sin embargo, los 10nm ya son una realidad para algunas fundiciones:

- Intel espera producir en masa los primeros chips (Cannon Lake) de 10nm en la segunda mitad del 2018.

- Samsung lleva desde abril de 2017 con el Galaxy S8, un smartphone con el primer procesador basado en su propio proceso de 10nm.

- TSMC dio a luz a los 10nm con el SoC Apple A10X que integran los iPads Pro desde junio de 2017.

- Global Foundries prevé saltarse los 10nm e ir directos a los 7nm.

Viendo esto parece ser que Intel se ha quedado atrás con respecto a los 10nm, sin embargo, tenemos que recordar que 10nm son nombres de marketing y no hacen referencia a medidas reales ni comparables entre fundiciones. Los datos reales son así:

Según esta tabla, el proceso de 14nm de Intel son en realidad nodos estándar de 13 cuando los procesos de 10nm de Samsung y TSMC son en realidad nodos estándar de 12nm. Por lo tanto, no hay gran diferencia entre el proceso de 14nm de Intel con respecto a los nuevos procesos de 10nm de Samsung y TSMC teniendo en cuenta además que Intel lleva produciendo chips a 14nm desde 2014.

No es ningún secreto que Intel, sea cual sea el número en nanómetros con el que llamen a su tecnología, tiene un claro liderazgo mundial en procesos de fabricación, y así ha sido durante décadas. No obstante, el reto que representa bajar de los 10nm (nodo estándar) hace probable que el Intel pierda su histórico reinado. Lo explicamos con detalle en el siguiente apartado.

¿Estamos ante el fin del liderazgo de Intel?

Durante las últimas décadas Intel ha reinado en el mundo de los semiconductores con soltura. Su gran ventaja en su exclusivo proceso de fabricación y el gran trabajo diseñando sus arquitecturas les ha permitido ir varios años por delante en cuanto a densidad de transistores y rendimiento por vatio se refiere con respecto a otras fundiciones. En esto se ven afectadas por tanto las demás marcas de procesadores, CPUs y SoCs que tienen que ver sus productos fabricados en procesos de fabricación que están menos avanzados que los de Intel.

Gracias a esta ventaja Intel lleva años manteniendo una aplastante cuota de mercado, muy por encima del 50% en CPUs de escritorio, CPUs profesionales, CPUs de portátiles y CPUs de servidor. Ir por delante y tener estas cuotas de mercado le han permitido además posicionarse en precio muy por encima de sus competidores, multiplicando sus beneficios. Prueba de ello son los 58 mil millones de dólares en beneficio que tuvieron en 2016. No nos cabe duda de que todo esto se debe en gran parte a su liderazgo en el proceso de fabricación.

Dicho esto volvamos a ponernos en la situación actual, usando las tecnologías fotolitográficas actuales basadas en silicio resulta muy difícil mejorar el proceso de fabricación. Hay que optar por algo distinto, por materiales o tecnologías nuevas.

Para bajar de los 10nm se especula que Intel han podido optar por litografía EUV (Extreme Ultra Violet) o bien ha decidido dar carpetazo al silicio por fotolitografía y desarrollar sus chips con nanotubos de carbono. En ambos casos estamos hablando de algo tan avanzado que le ha supuesto muchos años de investigación y la inversión de 7 mil millones de dólares en una nueva fábrica para ello. Esta nueva fábrica se encargará de la fabricación de chips de 7nm (5.9nm de nodo estándar) y se espera que entre en funcionamiento en el segundo semestre de 2021.

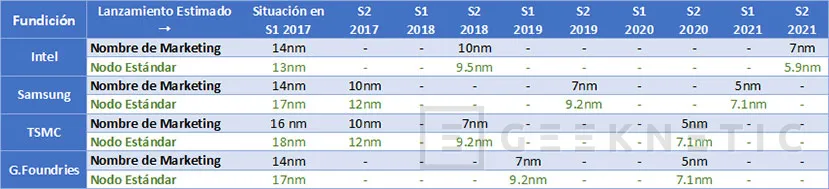

En la siguiente tabla comparamos los avances esperados en el tiempo por parte de las 4 fundiciones. Para ver el adelanto tecnológico real hacemos la comparación tanto con el nombre de marketing que le dan al nodo, como al nodo estándar siguiendo la fórmula ASML.

Como hemos visto en el apartado anterior y podemos apreciar también esta tabla los 10nm de Samsung y TSMC, que ya están en el mercado, no suponen una pérdida de liderazgo para los 14nm de Intel porque realmente si nos fijamos en el nodo estándar de ambos apenas hay diferencia.

Ya que no podemos fijarnos en el nombre que dan al proceso de fabricación para comparar el avance tecnológico de las fundiciones, las conclusiones que vienen a continuación estarán basadas únicamente en los cálculos estimados de nodo estándar según la fórmula ASML.

Se espera que a mitad de 2018 Intel tenga ya sus primeros chips a 9.5nm de nodo estándar, al mismo tiempo que TSMC tendrá nodos estándar de 9.2nm (llamados por ellos 10nm y 7nm respectivamente). En este caso tampoco supone una diferencia suficientemente sustancial como para poner en entredicho el liderazgo de Intel. Tampoco veremos a Intel superada en 2019, cuando lleguen los nuevos procesos Samsung y de Global Foundries, cuyo nodo estándar se estima también en 9.2nm.

Lo que cambia las tornas es el hecho de que Intel no dará el siguiente salto hasta finales de 2021 (7nm, pero nodo estándar de 5.9nm). Un año antes, en 2020, se estima que lleguen los procesos TSMC y Global Foundries con nodo estándar de 7.1nm (pese a que ellos los llamen procesos de 5nm). En ese momento a Intel, a la espera de la puesta en marcha de su nueva fábrica, no le quedará otro remedio que hacerles frente en el mercado con chips de 9.5 en nodo estándar, considerablemente inferiores en densidad de transistores a los de 7.1nm en nodo estándar que proporcionarán los procesos que sus competidores llaman de 5nm.

Esto a Intel le puede suponer por tanto dejar el trono de los procesos de fabricación, al menos durante 1 año.

Pese a que esto suene como algo catastrófico para Intel, no podemos olvidar que la cuota de mercado y su imagen de marca no va a cambiar de un día para otro y en el peor de los casos estarán solo 1 año fuera del trono tras décadas de liderazgo.

Para no perder cuota de mercado tal vez tengan que bajar precios ligeramente, aunque una arquitectura mejorada y depurada lo puede compensar. Un ejemplo a tener en cuenta es el hecho de que AMD con su arquitectura Zen está consiguiendo dar a Intel unos cuantos dolores de cabeza, y eso que el proceso de 14nm (17nm nodo estándar) de Global Foundries en el que fabrica AMD, es considerablemente peor en densidad de transistores al proceso de 14nm (13nm nodo estándar) de Intel. Quién nos dice que Intel no pueda hacer lo mismo cuando se vean en desventaja en su proceso de fabricación.

Nota: Algunos de los datos de este artículo son estimaciones y predicciones que no se han de tomar con exactitud.

Nota2: Buena parte de los datos, informaciones y mediciones utilizadas en este artículo han sido facilitadas ASML, IC Knowledge, SemiWiki y Seeking Alpha.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!