AMD mezclará proceso de 2 nm para los CCDs y de 3 nm para el chip de E/S en sus próximos procesadores con núcleos Zen 6

por Juan Antonio SotoCon una buena base ya establecida de procesadores AMD con núcleos Zen 5, tanto para servidores y centros de datos como para equipos domésticos, al fabricante no le queda otra que seguir avanzando para poder continuar con el éxito que viene acumulando en los últimos años. Los rumores citaban que AMD fabricaría los procesadores con Zen 6 bajo los nodos de 2 y 3 nanómetros de TSMC, algo que Kepler nos ha dejado más claro.

AMD combinará procesos de 2 y 3 nm en sus próximos procesadores

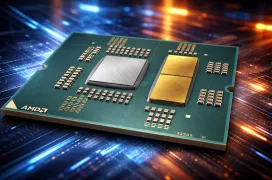

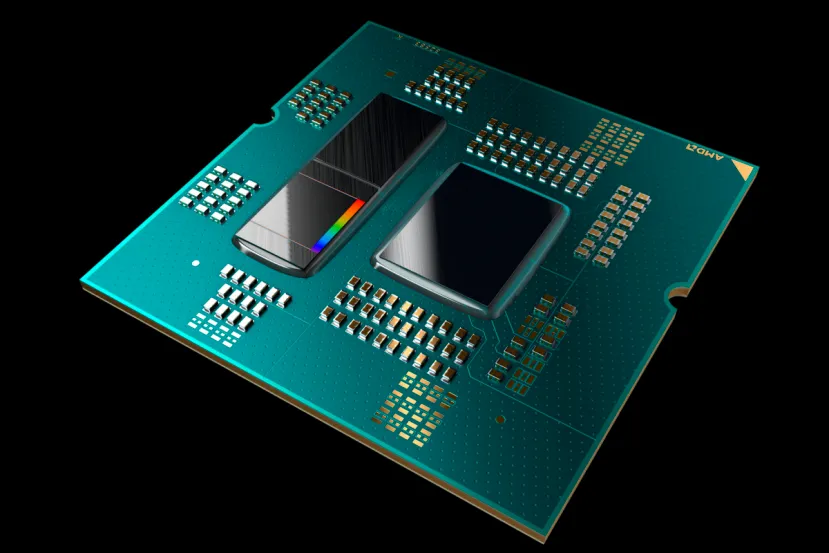

Según este conocido filtrador, el proceso más avanzado de 2 nanómetros estará destinado a la fabricación de los CCDs con los núcleos Zen 6, mientras que el proceso de 3 nanómetros se usará para la baldosa de E/S. Concretamente para la fabricación de los CCDs con núcleos Zen 6 se usará el proceso avanzado de TSMC N2P, y para el chip de E/S se usará el N3P. Una combinación de ambos nodos que aprovechará las ventajas de ambos para fusionar en los futuros procesadores de AMD.

Los rumores cuentan que esta próxima generación de procesadores de AMD puede aumentar el número de núcleos por cada CCD. Actualmente encontramos procesadores con 8 núcleos Zen 5 por cada CCD, algo que puede cambiar a 12 núcleos con los próximos Zen 6. En este caso podemos encontrar procesadores que integren 2 CCDs con 12 núcleos cada uno, para un total de 24 núcleos que además serán compatibles con SMT y obtener 48 hilos de ejecución.

Los nuevos CCDs podrán llevar hasta 12 núcleos, que darán vida a procesadores de 24 núcleos y 48 hilos

La fabricación bajo este nodo avanzado N2P de TSMC permitirán a AMD obtener núcleos con velocidades de reloj más altas junto con mayor eficiencia energética. El objetivo con esta nueva generación es la de obtener un incremento de IPC de dos cifras. Por otra parte, el nodo N3P para la baldosa de E/S alojará el controlador de memoria, las líneas PCIe, los USB e incluso la GPU integrada. Bajo este nodo se puede conseguir una reducción del coste de fabricación, mientras que para los CCDs se ha primado el rendimiento y la eficiencia.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!