SK hynix da un salto en DDR5: el nuevo chip A-die AKBD de 3 GB apunta a 7200 MT/s y marca el relevo de los M-die

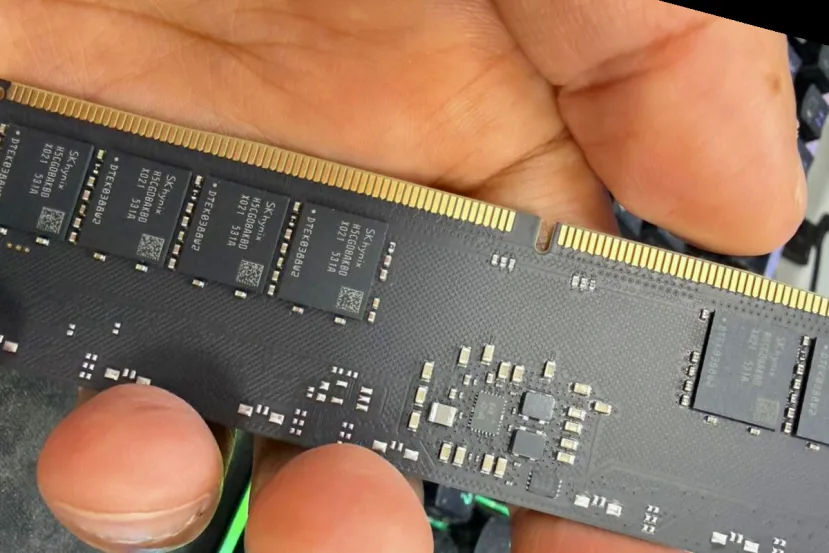

por Manuel NaranjoLas filtraciones con nombre y apellidos suelen ser las más interesantes porque permiten leer entre líneas. Un módulo DDR5 con serigrafía X021 y código AKBD ha aparecido en fotos compartidas por Kevin Wu (Team Group). La pista que completa el puzle la aporta @unikoshardware: se trataría del nuevo A-die de 3 GB de segunda generación de SK hynix, el sucesor natural de los M-die que han dominado la primera etapa de la DDR5.

De EB a KB: cómo se lee el “AKBD”

SK hynix ha sido bastante consistente en sus etiquetas internas. Las terminaciones EB, FB, GB o HB han ido marcando escalones en frecuencia JEDEC nativa: 4.800, 5.600, 6.000/6.200 y 6.400 MT/s, respectivamente. Si el nuevo chip luce “KB”, la interpretación más razonable es 7.200 MT/s de base. Esto no es un perfil XMP/EXPO elevado artificialmente, sino una indicación de lo que el silicio puede sostener dentro de la especificación estándar, con voltajes y timings conservadores.

Densidad de 3 GB por chip: qué implica para la capacidad

Que se hable de 3 GB por IC no es un capricho: condiciona la topología de los módulos. En DDR5, lo habitual son 2 GB y 4 GB. Con 3 GB, un DIMM de 16 chips ofrece 48 GB; con 8 chips, 24 GB. Esto encaja con el auge de kits 2×24 GB (48 GB) y 2×48 GB (96 GB) que ya hemos visto con M-die, proporcionando un punto dulce entre capacidad y latencia frente a los populistas 2×32 GB. Si el nuevo A-die hereda el buen comportamiento de M-die con densidades intermedias, podríamos ver kits 2×24 GB a 7.200–7.600 MT/s estables con perfiles razonables sin necesidad de escaladas de voltaje agresivas.

PCB de 8 capas en la muestra: un techo para el overclock… y un mensaje al mercado

La unidad filtrada monta PCB de 8 capas. Es suficiente para clavar 7.200 MT/s JEDEC y para perfiles algo más alegres, pero no es el terreno ideal para el overclock extremo por encima de 8.000 MT/s. Para eso, los fabricantes suelen pasar a 10 o 12 capas, que mejoran la integridad de señal, la diafonía entre líneas y la distribución de potencia del PMIC.

DDR5 ha aprendido a fuerza de iteraciones que más MHz no siempre significa mejor latencia efectiva. La clave está en el tRFC, tFAW, tRCD y tCCD_L que los perfiles XMP/EXPO fijan para cuadrar frecuencia y estabilidad. Los M-die ya demostraron que podían sostener CL34–36 a 7.200–7.600 con 1,35–1,40 V en kits bien binados. Si el A-die AKBD escala igual o mejor, veremos perfiles JEDEC de 7.200 con timings relajados para compatibilidad universal y, en paralelo, perfiles XMP con latencias más agresivas en las gamas entusiastas.

PMIC, temperaturas y la otra mitad del rendimiento

La estabilidad de un módulo DDR5 ya no depende solo del IC; el PMIC on-DIMM y el sistema térmico (disipador, almohadillas, flujo de aire) juegan un papel igual de determinante. A 7.200–7.800 MT/s, el PMIC trabaja con transitorios de corriente más exigentes; si SK hynix ha optimizado las curvas de consumo del A-die, los módulos podrán mantener frecuencias altas durante cargas sostenidas sin “thermal throttling” silencioso. De ahí que muchos kits premium combinen estos chips con disipadores de mayor masa o incluso barras con caloductos, no por estética, sino para estabilizar las variaciones térmicas que alteran la señal.

Por qué SK hynix domina ahora donde antes reinaba Samsung

En DDR4, decir “B-die” era sinónimo de latencias bajas y escalado limpio; los overclockers lo convirtieron en una religión. Con DDR5, Samsung perdió ese halo por una combinación de proceso, madurez de controladores y, sobre todo, la rapidez con la que SK hynix afinó sus M-die. Si el A-die de segunda generación se confirma como un silicio que sube la base a 7200 y mantiene una curva de voltaje favorable, SK hynix consolidará un liderazgo que, a estas alturas, ya no parece coyuntural.

Qué cabe esperar en el corto plazo

Lo más sensato es anticipar kits 2×24 GB y 2×48 GB a 7.200–7.600 MT/s como primera hornada, con PCBs de 8 capas para volumen y un precio cercano a las gamas medias-altas actuales. A partir de ahí, veremos ediciones con 10/12 capas y perfiles XMP más ambiciosos para cruzar 8.000–8.200 MT/s con estabilidad en placas Z de nueva generación.

El AKBD A-die no pretende romper récords de validación; pretende convertir 7.200 MT/s en el nuevo suelo de la memoria premium de consumo. Si a esa base le sumas kits bien diseñados, PCBs de más capas cuando toque y firmware maduro en placas y CPU, el resultado es un ecosistema donde el ancho de banda deja de ser el cuello de botella y la latencia efectiva vuelve a ser el campo de batalla. SK hynix ya tiene la inercia a favor; si este chip cumple lo que su etiqueta sugiere, el dominio en DDR5 seguirá ampliándose, y el usuario ganará en algo que a menudo se olvida: previsibilidad. Abrir la caja, montar, cargar XMP y listo.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!